# 68000 Interrupt Controller

Danesh Tavana

Commercial and industrial microprocessor-based systems consist of the basic block units of CPU, memory, and I/O devices. While executing instructions in memory, the CPU must somehow be interrupted to service requests from various I/O devices. The 68000 microprocessor is a powerful 16-bit processor which makes provisions for 256 different interrupt routines. A simple and cost-effective way of interfacing a peripheral's interrupt request signal to the CPU is through Programmable Array Logic. This paper introduces two ways of designing such an interface with PAL devices.

# **68000 Interrupt Controller**

Danesh Tayana

#### Introduction

Commercial and industrial microprocessor-based systems typically consist of a processor interfaced with many peripherals which randomly require service. To fully utilize the processor's computing potential, sources of hardware interrupts must be used to free the processor from software routines. The 68000 16-bit microprocessor has 256 different exception-processing vectors which point to predetermined locations in the program memory space. There are 192 external user interrupt vectors and seven autovector interrupts. Table 1 shows the exception vector assignments. The interrupt structure of the 68000 will be discussed in more detail along with two methods of designing an

| Vector    |      | Addres |       |                                |

|-----------|------|--------|-------|--------------------------------|

| Number(s) | Dec  | Hex    | Space | Assignment                     |

| 0         | 0    | 000    | SP    | Reset: Initial SSP             |

|           | 4    | 004    | SP    | Reset: Initial PC              |

| 2         | 8    | 008    | SD    | Bus Error                      |

| 3         | 12   | OOC    | SD    | Address Error                  |

| 4         | 16   | 010    | SD    | Illegal Instruction            |

| 5         | 20   | 014    | SD    | Zero Divide                    |

| 6         | 24   | 018    | SD    | CHK Instruction                |

| 7         | 28   | 01C    | SD    | TRAPV Instruction              |

| 8         | 32   | 020    | SD    | Privilege Violation            |

| 9         | 36   | 024    | SD    | Trace                          |

| 10        | 40   | 028    | SD    | Line 1010 Emulator             |

| 11        | 44   | 02C    | SD    | Line 1111 Emulator             |

| 12*       | 48   | 030    | SD    | (Unassigned, reserved)         |

| 13*       | 52   | 034    | SD    | (Unassigned, reserved)         |

| 14*       | 56   | 038    | SD    | (Unassigned, reserved)         |

| 15        | 60   | 03C    | SD    | Uninitialized Interrupt Vector |

| 16-23*    | 64   | 04C    | SD    | (Unassigned, reserved)         |

|           | 95   | 05F    |       | _                              |

| 24        | 96   | 060    | SD    | Spurious Interrupt             |

| 25        | 100  | 064    | SD    | Level 1 Interrupt Autovector   |

| 26        | 104  | 068    | SD    | Level 2 Interrupt Autovector   |

| 27        | 108  | 06C    | SD    | Level 3 Interrupt Autovector   |

| 28        | 112  | 070    | SD    | Level 4 Interrupt Autovector   |

| 29        | 116  | 074    | SD    | Level 5 Interrupt Autovector   |

| 30        | 120  | 078    | SD    | Level 6 Interrupt Autovector   |

| 31        | 124  | 07C    | SD    | Level 7 Interrupt Autovector   |

| 32-47     | 128  | 080    | SD    | TRAP Instruction Vectors       |

|           | 191  | OBF    |       |                                |

| 48-63*    | 192  | 0C0    | SD    | (Unassigned, reserved)         |

|           | 255  | 0FF    |       |                                |

| 64-255    | 256  | 100    | SD    | User Interrupt Vectors         |

|           | 1023 | 3FF    |       | _                              |

<sup>\*</sup>Vector numbers 12, 13, 14, 16 through 23 and 48 through 63 are reserved for future enhancements by Motorola. No user peripheral devices should be assigned these numbers.

Table 1. Exception Vector Assignment

interrupt controller using PAL devices (Programmable Array Logic).

# 68000 Exception Processing and Pin Description

The interrupt structure of the 68000 can grant up to 256 types of interrupt requests. These interrupts, or exceptions, are generated either by external or internal causes and are serviced by directing the flow of program to an exception processing routine. Table 1 lists these exceptions and their respective address in memory. Exception vectors are locations in memory where the processor fetches the address of a routine or subprogram which will service that exception. The exception vector is either internally or externally generated depending on the cause of the interrupt. The externally generated exceptions are interrupts which are placed on the interrupt control pins (IPL2, IPL1 and IPL0), bus errors, and reset requests. The interrupts placed on control pins IPL2-IPLO are requests from peripheral devices. The internally-generated exceptions come from instructions, address errors, or tracing. These different types of exceptions and their priorities are shown in Table 2. We will focus on group 1 interrupt exceptions.

| Group | Exception                               | Processing                                                       |  |  |  |  |  |

|-------|-----------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| 0     | Reset<br>Bus Error<br>Address Error     | Exception processing begins within two clock cycles.             |  |  |  |  |  |

| 1     | Trace<br>Interrupt<br>Illegal Privilege | Exception processing begins before the next instruction.         |  |  |  |  |  |

| 2     | TRAP, TRAPV,<br>CHK,<br>Zero Divide     | Exception processing is started by normal instruction execution. |  |  |  |  |  |

Table 2. Exception Grouping and Priority

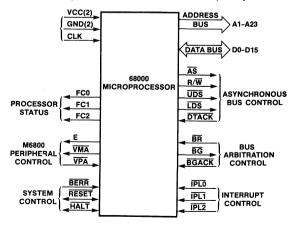

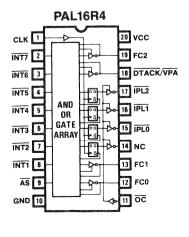

The pinout of the 68000 is shown in Figure 1. The three interrupt control pins (IPL2, IPL1, IPL0) are asynchronous active low inputs which indicate the encoded priority level of

Figure 1.

the device requesting an interrupt. The least significant bit is IPLO and the most significant bit is IPL2. Level seven, (IPL2, IPL1, IPL0) = (000), has the highest priority, while level zero. (111), indicates that no interrupts are requested. All lower or equal priority interrupts are masked during the interrupt service routine of the present interrupting device. There are two ways by which a peripheral device can interrupt the normal flow of program; autovectoring or external vector number generation. The function code pins (FC2, FC1, and FC0) all become high during an interrupt acknowledge cycle. The interrupt acknowledge cycle always follows an interrupt request only after the present instruction cycle is completed. Thus interrupt acknowlede cycles come in between the instruction cycles and no information is lost.

The signals which are used during an external interrupt request are listed below with a description of their behavior and function.

ADDRESS BUS: The 24-bit address bus holds the address of the data to be accessed. During an interrupt acknowledge cycle the lower three bits (A3 A2 A1) hold the encoded level of the interrupt being serviced. If a level 5 interrupt is being serviced then (A3 A2 A1) will be (101) respectively.

DATA BUS: The lower eight bits of this 16-bit data bus must contain the vector number during a user interrupt acknowledge cycle. If an autovector routine is in process then the data bus is ignored.

AS: The processor asserts address strobe anytime there is valid data on the address bus. It remains asserted for as long as the address is valid.

R/W: This signal defines the data bus transfer as a read or a write cycle. During an interrupt acknowledge cycle the processor is in a read mode.

UDS, LDS: The upper and lower data strobes are asserted when the processor is in a read or write instruction cycle. Upper stobe enables the most significant byte of data while the lower stobe enables the least significant.

**DTACK:** Data transfer acknowledge is an externally generated signal which tells the processor that valid data is present on the data bus. If DTACK is not asserted before the falling edge of S4 (S4 is the fourth CPU clock state in a seven-state instruction cycle) then wait states are introduced.

IPL2-IPL0: The three interrupt control pins are inputs which contain the encoded priority level of the external interrupting device. Note that these are active low pins where (000) is level seven encoded.

FC2-FC0: Function code output pins indicate the processor's status. When they are all high the processor is in an interrupt acknowledge cycle.

E, VMA, VPA: Enable, valid memory address, and valid peripheral address are the standard 6800 family signals. VPA is also used when autovectoring.

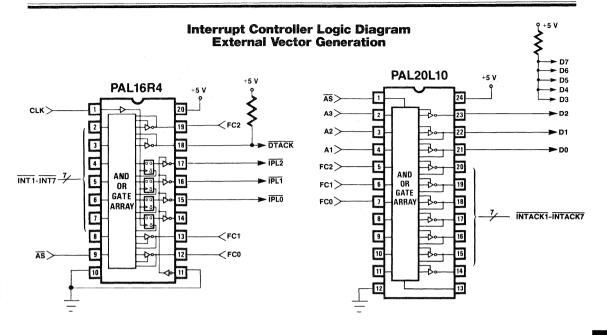

The following two design examples use PAL units as a simple and cost-effective interrupt controller interface to the 68000. The first introduces external vector generation while the second shows how autovectoring can be done on the 68000.

# **Prioritized Individually Vectored** Interrupt (Method 1)

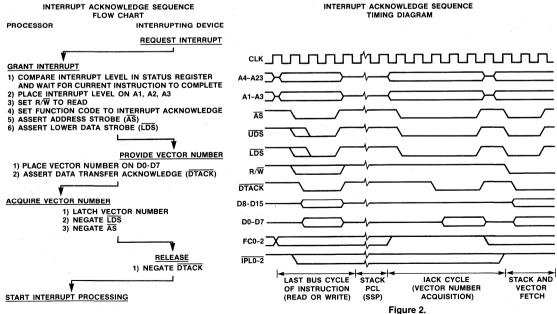

As shown in the interrupt acknowledge sequence flow chart and timing diagram (Figure 2), a peripheral device must interrupt the processor by placing the encoded level of priority on the interrupt control pins (IPL2-IPL0). The processor then grants the interrupt after the completion of the current instruction cycle. The encoded priority level of the interrupt is placed on address bus bits A3-A1 during the interrupt acknowledge cycle. The status code lines (FC2-FC0) become high, indicating an interrupt acknowledge cycle. Once the lower data strobe (LDS) is asserted the external device must place an 8-bit vector on the least significant byte of the data bus. This data is latched in state S7.

INTERRUPT ACKNOWLEDGE SEQUENCE

As shown on Table 1 vectors 64-255 are assigned to the user interrupt vector numbers. These vectors must be generated externally and placed on the data bus during an interrupt acknowledge cycle. In our interrupt controller we arbitrarily choose vectors 249-255 as the vectors assigned to the interrupting peripheral devices. Table 3a shows this assignment and how the vector can be decoded from the address bits A1-A3.

| Priority<br>level | Vector assigned | Data |     |    |    |    |    |    | Address |    |    |     |

|-------------------|-----------------|------|-----|----|----|----|----|----|---------|----|----|-----|

| Device #          | Decimal #       | D7   | D6  | D5 | D4 | D3 | D2 | D1 | D0      | А3 | A2 | Α1  |

| 1 (low priority)  | 249             | 1    | 1   | 1  | 1  | 1  | 0  | 0  | 1       | 0  | 0  | 1   |

| 2                 | 250             | 1    | 1   | 1  | 1  | 1  | 0  | 1  | 0 ·     | 0  | 1  | 0   |

| 3                 | 251             | 1    | 1   | 1  | 1  | 1  | 0  | 1  | 1       | 0  | 1  | 1   |

| 4                 | 252             | 1    | 1   | 1  | 1  | 1  | 1  | 0  | 0       | 1  | 0  | 0 . |

| 5                 | 253             | - 1  | . 1 | 1  | 1  | 1  | 1  | 0  | 1       | 1  | 0  | 1   |

| 6                 | 254             | 1    | 1   | 1  | 1  | 1  | 1  | 1  | 0       | .1 | 1  | 0   |

| 7 (high priority) | 255             | 1    | 1   | 1  | 1  | -1 | 1  | 1  | 1       | 1  | 1  | 1   |

Table 3a.

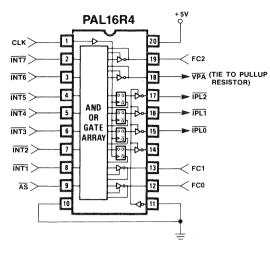

The two PALs used on this design example generate the interrupt vectors and all the necessary control signals. The various signals and their implementation on the PALs are explained below.

INT7-INT0: Any of the seven peripheral devices can request an interrupt by asserting one of these inputs. The interrupt must remain asserted until acknowledged by the CPU.

FC2-FC0 and  $\overline{\rm AS}$ : Function code or processor status code become logical high during an interrupt acknowledge cycle. Address strobe is asserted anytime valid address is on the bus.  $\overline{\rm DTACK}$  and Data output control are decoded from these four outputs of the 68000.

A1-A3: The three least significant bits of the address bus contain the encoded level of the interrupting device. These signals are used in generating the vector number which is to be put on the data bus.

**RESET:** Reset is an input which clears all outputs, and is used for system initialization.

**IPL2-IPLO:** These PAL outputs are active low synchronous signals which interface directly to the CPU. They represent the encoded level of the highest priority interrupt that is requested. Table 3b shows the truth table of our priority encoder implemented on a PAL.

| Interrupt request input from peripheral |      |      |      |      |      |      | Encoded int. level |      |             |  |

|-----------------------------------------|------|------|------|------|------|------|--------------------|------|-------------|--|

| INT7                                    | INT6 | INT5 | INT4 | INT3 | INT2 | INT1 | IPL2               | IPL1 | <b>IPLO</b> |  |

| 0                                       | X    | Х    | X    | X    | X    | X    | 0                  | 0    | 0           |  |

| 1                                       | 0    | Х    | Х    | Х    | Χ    | X    | 0                  | 0    | 1           |  |

| 1                                       | - 1  | 0    | Х    | Х    | Х    | Х    | 0                  | 1    | 0           |  |

| 1                                       | 1    | 1    | 0    | X    | X    | X    | l o                | 1    | 1           |  |

| 1                                       | 1    | 1    | 1    | 0    | X    | X    | 1                  | 0    | 0           |  |

| 1                                       | 1    | 1    | 1    | 1    | 0    | Х    | 1 1                | 0    | 1           |  |

| 1                                       | 1    | 1    | 1    | 1 .  | 1    | 0    | 1                  | 1    | 0           |  |

| 1                                       | 1    | 1    | 1    | 1    | 1    | 1    | 1                  | 1    | 1           |  |

Table 3b.

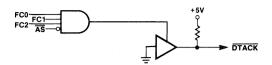

DTACK: Data transfer acknowledge must be asserted by outside circuitry during a data transfer operation. The logic diagram shown below illustrates how DTACK is derived from address strobe and processor status signals.

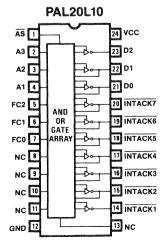

**D7-D0:** The three least significant bits of the data output can be decoded straight from the address bits A3, A2 and A1. That is D2=A3, D1=A2 and D0=A1. The other five bits of data can be held high with pull-up resistors. Outputs of the three data bits become enabled by using the same scheme which enables the DTACK output.

INTACK7-INTACK1: Only one of these signals will be asserted during the interrupt acknowledge cycle. This signal feeds back into the interrupting device to tell that device that its interrupt has been acknowledged. We can use the 3-bit addresses to decode these signals as shown in Table 3a.

|   |    |   |     | INTACK |     |   |   |     |   |  |

|---|----|---|-----|--------|-----|---|---|-----|---|--|

|   | A2 |   | 7   | 6      | 5   | 4 | 3 | 2   | 1 |  |

| 0 | 0  | 0 | . 1 | 1      | 1   | 1 | 1 | 1   | 1 |  |

| 0 | 0  | 1 | 1   | 1      | 1   | 1 | 1 | 1   | 0 |  |

| 0 | 1  | 0 | 1   | 1      | 1   | 1 | 1 | 0   | 1 |  |

| 0 | 1  | 1 | 1   | 1      | 1   | 1 | 0 | . 1 | 1 |  |

| 1 | 0  | 0 | 1   | 1      | 1   | 0 | 1 | 1   | 1 |  |

| 1 | 0  | 1 | 1   | 1      | 0   | 1 | 1 | 1   | 1 |  |

| 1 | 1  | 0 | 1   | 0      | . 1 | 1 | 1 | 1.  | 1 |  |

| 1 | 1  | 1 | 1 0 | 1      | 1   | 1 | 1 | 1   | 1 |  |

Table 3c.

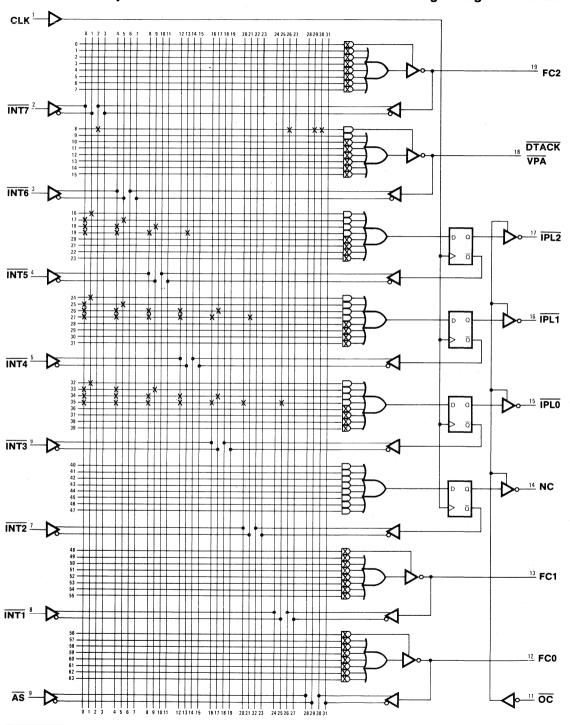

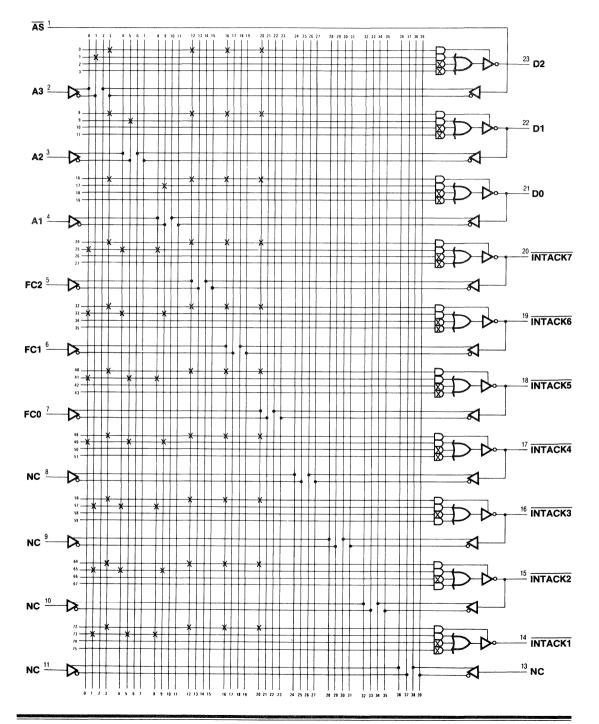

The logic diagram of the controller is shown in Figure 3. The controller can operate without any wait states at the fastest CPU clock rate of 12.5 MHz as shown in the timing diagram of Figure 4. The appendix contains the fuse plot which translates into a logic schematic for these two PALs.

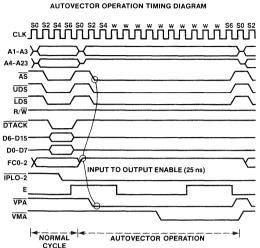

# **Auto-vectored Interrupts (Method 2)**

The seven autovector interrupts are assigned vector numbers 25 through 31. Interrupts are requested by placing the encoded level of the request on the interrupt control pins (IPL2-IPL0). The processor responds to this request by placing the requested level in the processor's status register and by inhibiting all requests of lower priority. When the current instruction cycle is completed an interrupt acknowledge cycle takes place. If Valid Peripheral Address (VPA) is asserted before the falling edge of S4 then an autovector routine takes place. The data or the vector number is generated internally depending on the priority level of the interrupt request; the vector assigned is shown on the table at the beginning of this report. The autovector timing diagram and a very simple and practical interrupt controller implemented on a PAL is shown in Figure 5. The PAL design specifications are included in the appendix. Note that VPA is generated by enabling the PAL output when FC2-FC1 are high and AS is asserted. The appendix contains the fuse plots for this PAL design. Note that the fuse plots translate directly to a logic diagram.

Figure 3. S1 S3 CLK ĀŜ UDS LDS R/W FC0-2 17 -10-D0-7 18 DTACK -12 IPL0-2 WRITE MACHINE CYCLE STACK PCL INTERRUPT ACKNOWLEDGE CYCLE STACK 8 CLOCK HIGH TO  $R/\overline{W}$  HIGH (60 ns) 9 CLOCK HIGH TO  $R/\overline{W}$  LOW (60 ns) 10 CLOCK HIGH TO FC VALID (55 ns) 15 DATA VALID TO DS LOW (15 ns)

16 CLOCK HIGH TO AS, DS LOW (55 ns)

17 PAL's INPUT TO Hi-Z (25 ns) 1 CLOCK PERIOD (80 ns) 2 CLOCK LOW TO ADDRESS (55 ns)

10 CLOCK HIGH TO DATA HI-Z (60 ns)

11 CLOCK HIGH TO DATA HI-Z (60 ns)

12 AS HIGH TO DTACK HIGH (70 ns)

13 PAL's CLOCK TO OUT (25 ns)

14 MINIMUM SETUP TIME (20 ns)

Figure 4.

2 CLOCK LOW 10 ADDRESS (55 ns)

3 CLOCK HIGH TO ADDRESS Hi-Z (60 ns)

4 CLOCK HIGH TO AS LOW (55 ns)

5 CLOCK LOW TO AS HIGH (50 ns)

6 CLOCK HIGH TO DS LOW (55 ns)

7 CLOCK LOW TO DS HIGH (50 ns)

18 PAL's INPUT TO Hi-Z (25 ns) 19 PAL's INPUT TO Hi-Z (25 ns)

Figure 5.

### Conclusions

We have just seen how to implement an interrupt controller circuit using one or two PAL devices. This circuit can operate at the maximum operating frequency of the 68000 which is 12.5 MHz. Since the most critical timing of the circuit is the PAL unit's input to Hi-Z, we see that we can operate the circuit with a wide spectrum of frequencies and with slower PAL devices. To guarantee operation, timing spec. No. 16 and No. 19 on Figure 4 must add up to assert DTACK 20 ns prior to falling edge of S4. Thus 55 ns + (PAL input delay to Hi-Z) should be less than, or equal to, 100 ns for a 12.5 MHz clock. We see that this qualifies fast, regular and half-power PAL devices for this circuit. At slower CPU clock rates even the quarter-power PAL devices may be used.

## **Appendix**

# **Interrupt Controller**

### References

- 1. J. Birkner, V. Coli, "PAL® Programmable Array Logic Handbook," Monolithic Memories Inc.

- MC68000 Data Sheet, Motorola Semiconductors. Austin, Texas 78721.

- 3. Rex Davis, "Prioritized Individually Vectored Interrupts for Multiple Peripheral Systems with the MC68000." Motorola Application Note AN-819

## Interrupt Controller

## **68000 Interrupt Controller**

```

PAL20L10

PAL DESIGN SPECIFICATIONS

INTC.DAT

DANESH TAVANA

9/25/82

INTERRUPT CONTROLLER

MMI, SUNNYVALE

/AS

A2

A1

FC2

FC1

FC0

NC

NC NC NC GND

A3

NC /INTACK1 /INTACK2 /INTACK3 /INTACK4 /INTACK5 /INTACK6 /INTACK7 D0 D1 D2 VCC

IF (FC2* FC1* FC0* AS) /D2 =/A3

IF (FC2* FC1* FC0* AS) /D1 =/A2

IF (FC2* FC1* FC0* AS) /D0 =/A1

IF (FC2*FC1*FC0*AS) INTACK7 = A3* A2* A1

IF (FC2* FC1* FC0* AS) INTACK6 = A3* A2*/A1

IF (FC2*FC1*FC0*AS) INTACK5 = A3*/A2*Al

IF (FC2*FC1*FC0*AS) INTACK4 = A3*/A2*/A1

IF (FC2* FC1* FC0* AS) INTACK3 =/A3* A2* A1

IF (FC2* FC1* FC0* AS) INTACK2 =/A3* A2*/A1

IF (FC2*FC1*FC0*AS) INTACK1 =/A3*/A2* A1

```

#### FUNCTION TABLE /AS FC2 FC1 FC0 A3 A2 A1 D2 D1 D0 /INTACK7 /INTACK6 /INTACK5 /INTACK4 /INTACK3 /INTACK2 /INTACK1 / / Ι Ι ; I Ι Ι Ι Ι N N N N N ; т Т T т т Α Α C ;/ F F С С С ССС K K K K K D D D K AAA :S 2 1 7 5 3 COMMENTS Н NO INTERRUPT L H H L L L L L H н н Η Η н н Н L Н Н Н Η L Н H Н L L L Н Η Η L LEVEL 1 Н H L Η L H Н Н Η Η L H LEVEL 2 L н н L Τ. L Н н н Н H L H H Н H Н Η L H H LEVEL 3 L т. Н н н н L т. H L L H H H Τ. н н н LEVEL 4 L Η Н Η Η L H Η L Η H H L Η н н н LEVEL 5 Н Η н н Н H Ĺ H Н Н H н н LEVEL 6 L Н L L L H н н н н н H н н L H Η H н н н LEVEL 7 Н Х X X $X \quad X \quad X$ $\mathbf{z} = \mathbf{z}$ Z z zZ Z Z z = zOUTPUT HI-Z L Η H L $X \quad X \quad X$ $\mathbf{z}$ Z Z Z Z $\mathbf{z}$ $\mathbf{z}$ OUTPUT HI-Z Η $X \quad X \quad X$ Z Z Z Z $\mathbf{z}$ L L H Z $\mathbf{z}$ $\mathbf{z}$ $\mathbf{z}$ Z OUTPUT HI-Z L Н $X \quad X \quad X$ Z Z Z Z Z OUTPUT HI-Z

# **PAL1** — Interrupt Controller

# Logic Diagram PAL20L10

```

PAL16R4

PAL DESIGN SPECIFICATIONS

INTA.DAT

DANESH TAVANA

INTERRUPT CONTROLLER

MMI SUNNYVALE, CA

CLK /INT7 /INT6 /INT5 /INT4 /INT3 /INT2 /INT1 /AS GND

FC1 NC /IPL0 /IPL1 /IPL2 /DTACK FC2 VCC

IF (FC2* FC1* FC0* AS) DTACK = VCC

;ASSERT IF OUTPUT ENABLE

IPL2 := INT7

; PRIORITY ENCODED BIT

+ /INT7* INT6

+ /INT7*/INT6* INT5

+ /INT7*/INT6*/INT5* INT4

IPL1 := INT7

; PRIORITY ENCODED BIT

+ /INT7* INT6

+ /INT7*/INT6*/INT5*/INT4* INT3

+ /INT7*/INT6*/INT5*/INT4*/INT3* INT2

IPLO := INT7

; PRIORITY ENCODED BIT

+ /INT7*/INT6* INT5

+ /INT7*/INT6*/INT5*/INT4* INT3

+ /INT7*/INT6*/INT5*/INT4*/INT3*/INT2* INT1

```

#### FUNCTION TABLE

```

CLK /INT7 /INT6 /INT5 /INT4 /INT3 /INT2 /INT1

FC2 FC1 FC0 /AS /IPL2 /IPL1 /IPL0 /DTACK

1111111

III T

IIIIIII

;C NNNNNNN FFF/

PPPA

L TTTTTT CCCA

LLLC

;K 7654321

210S 210 K

COMMENTS

-----

C L X X X X X X H H H L L L L L C H L X X X X X H H H H H L L H Z

ASSERT /DTACK

INTERRUPT LEVEL 7

LLHL

LHLZ

CHHLXXXX

INTERRUPT LEVEL 6

LHLL

CHHHLXXX

LHHZ

INTERRUPT LEVEL 5

C H H H H L X X L H H L

HLLZ

INTERRUPT LEVEL 4

C H H H H H L X H L L L H L H Z

INTERRUPT LEVEL 3

С нинини ь

HHLZ

HLHL

INTERRUPT LEVEL 2

нин г

С нннннн

HHLL

INTERRUPT LEVEL 1

```

# **PAL2** — Interrupt Controller

# Logic Diagram PAL16R4